# 2.8W I2S 输入单声道D类音频功率放大器

### 2.8W I<sup>2</sup>S Input Mono Class D Audio Amplifier

#### **■** FEATURES

· Power Supply PVDD: 2.5-6.5V; DVDD/AVDD: 3.3V

Flexible Audio I/O

- I2S, LJ, RJ, TDM input

- 8, 16, 32, 44.1, 48, 88.2, 96, 192kHz Sample Rates

· Output Power

1.40W (PV<sub>DD</sub>=3.6V,  $R_L$ =4 $\Omega$ , THD+N=10%) 2.80W (PV<sub>DD</sub>=5.0V,  $R_L$ =4 $\Omega$ , THD+N=10%) 4.70W (PV<sub>DD</sub>=6.5V,  $R_L$ =4 $\Omega$ , THD+N=10%)

- THD+N= 0.08% (Po=1W,  $R_L$ =4 $\Omega$ ,  $PV_{DD}$  = 3.7V)

- · Adjustable Gain

- Clock Error, Over Current, Undervoltage, and Overtemperature Protection n

- Pb-free Packages, QFN4×4-20L

· 电源供电:

PVDD 2.5-6.5V; DVDD/AVDD 3.3V

- ·灵活的音频输入:

- I2S, LJ, RJ, TDM 输入

- 8, 16, 32, 44.1, 48, 88.2, 96, 192kHz 采样频

#### 率・输出功率:

1.40W (PV<sub>DD</sub>=3.6V,  $R_L$ =4 $\Omega$ , THD+N=10%) 2.80W (PV<sub>DD</sub>=5.0V,  $R_L$ =4 $\Omega$ , THD+N=10%) 4.70W (PV<sub>DD</sub>=6.5V,  $R_L$ =4 $\Omega$ , THD+N=10%)

- THD+N= 0.08% (Po=1W,  $R_L$ =4 $\Omega$ ,  $PV_{DD}$  = 3.7V)

- ・増益可调

- ·保护: 时钟错误、过流、欠压、过温保护等

- ·QFN4×4-20L封装

#### APPLICATIONS

· Smart Home · Smart Toys

・智能家居 ・智能玩具 · IoT设备

· IoT Devices 游戏设备·智能音箱·其他锂电/5V设备 Gaming Devices

· Smart Speakers · Other Li-ion cell/5V Devices

#### ORDERING INFORMATION

| Part Number | Package Type | Marking | Operating Temperature Range | MOQ/Shipping Package |

|-------------|--------------|---------|-----------------------------|----------------------|

| HT513SQER   | QFN4×4-20L   | HT513   | -40℃~85℃                    | Advance book only    |

#### **■** DESCRIPTION

The HT513 is an easy-to-use, low-cost, I<sup>2</sup>S input mono Class D audio amplifier that drives up to continuous 2.8W into 4ohm speaker with 5V power supply, and 4.7W into 4ohm speaker with 6.5V power supply.

HT513 integrates an DA converter, the  $I^2S$  interface supports up to 32bit width, 192kHz sample rate.

The built-in Class D amplifier also integrates Anti-clipping Function (ACF). The gain of the amplifier is also adjustable using external resistors.

The Device is available in QFN4×4-20L package.

HT513是一款低成本的I<sup>2</sup>S输入单声道输出D类音频功率放大器。其在5V供电时可提供最大2.8W的输出功率;在6.5V供电时可提供最大4.7W的输出功率。

HT513内部集成了DA转换器,其I<sup>2</sup>S输入最大支持32-bit字节,并且可自动监测采样频率,最高支持192kHz。

HT513集成的D类音频功放还具有增益可调、 防破音等功能。

该产品提供QFN4×4-20L封装。

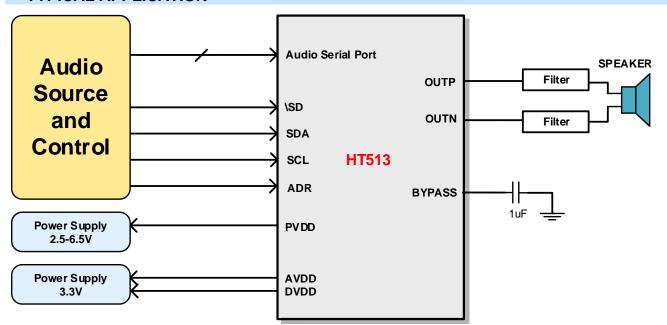

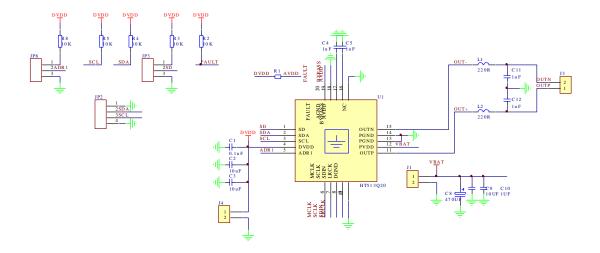

#### **■ TYPICAL APPLICATION**

-2-

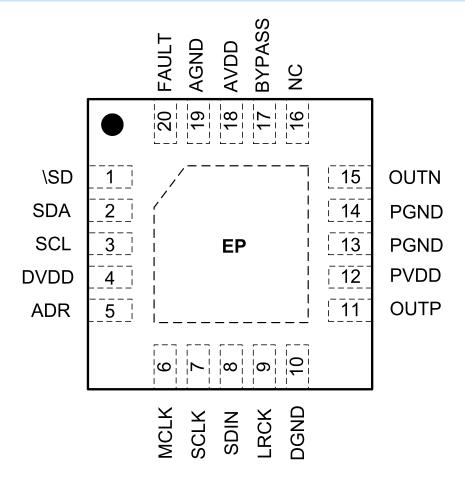

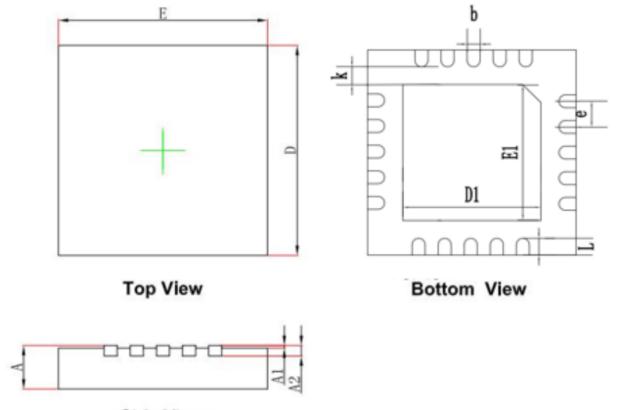

### **■ TERMINAL CONFIGURATION**

Top View

### **■ TERMINAL FUNCTION**

| Terminal No. | Name | I/O¹ | Description                                                                                                |

|--------------|------|------|------------------------------------------------------------------------------------------------------------|

| 1            | \SD  | I    | Places the speaker amplifier in shutdown mode while pulled low level. 接地时功放关闭                              |

| 2            | SDA  | I    | I <sup>2</sup> C data input pin. I2C 数据                                                                    |

| 3            | SCL  | I    | I <sup>2</sup> C clock input terminal. I2C 时钟                                                              |

| 4            | DVDD | P    | Power supply for the internal digital circuitry. 数字电源端                                                     |

| 5            | ADR  | I    | Determine the I <sup>2</sup> C Address of the device. I2C 器件地址选择                                           |

| 6            | MCLK | I    | Master Clock used for internal clock tree, sub-circuit/state machine, and Serial Audio Port clocking. 主时钟  |

| 7            | SCLK | I    | Bit clock for the digital signal that is active on the serial data port's input data line. 串 行时钟           |

| 8            | SDIN | I    | Data line to the serial data port. 串行数据                                                                    |

| 9            | LRCK | I    | Word select clock for the digital signal that is active on the serial port's input data line. 帧时钟,字段(声道)选择 |

| 10           | DGND | G    | Ground for digital circuitry (NOTE: This pin should be connected to the system ground). 数字地                |

| 11           | OUTP | О    | Positive pin for differential speaker amplifier. 功放输出正端                                                    |

| 12           | PVDD | P    | Power Supply for internal power circuitry.功率电源                                                             |

| 13, 14       | PGND | G    | Ground for power device circuitry. 功率地                                                                     |

| 15           | OUTN | О    | Negative pin for differential speaker amplifier. 功放输出负端                                                    |

-3-

# HT513 I<sup>2</sup>S input Class D Amplifier

| 16 | NC     | 1 | No Connection. Connect to GND for thermal dissipation. 无连接,可接地,增加散热                                                           |

|----|--------|---|-------------------------------------------------------------------------------------------------------------------------------|

| 17 | BYPASS | О | Analog reference terminal for Class D Amp. D 类功放模拟参考电压。                                                                       |

| 18 | AVDD   | P | Power supply for internal analog circuitry. 模拟电源端                                                                             |

| 19 | AGND   | G | Ground for analog circuitry (NOTE: This pin should be connected to the system ground). 模拟地                                    |

| 20 | FAULT  | 0 | Speaker amplifier fault terminal, which is pulled LOW when an internal fault occurs, open-drain output. 错误状态位,芯片发生某些错误时,该引脚拉低 |

| EP | -      | - | No connection, provides thermal connection from the device to the board. 内部无连接,为器件散热通道。                                       |

### ■ SPECIFICATIONS<sup>1</sup>

### Absolute Maximum Ratings<sup>2</sup>

| PARAMETER                              | Symbol           | MIN  | TYP  | MAX      | UNIT       |

|----------------------------------------|------------------|------|------|----------|------------|

| Power supply voltage for AVDD          | AVDD             | -0.3 |      | 4        | V          |

| Power supply voltage for PVDD          | PVDD             | -0.3 |      | 7        | V          |

| Power supply voltage for DVDD          | DVDD             | -0.3 |      | 4        | V          |

| DVDD Referenced Digital Input Voltages | Vı               | -0.3 |      | DVDD+0.3 | V          |

| Moisture Sensitivity Level (MSL)       |                  |      | MSL3 |          |            |

| Ambient Operating Temperature          | TA               | -25  |      | 85       | °C         |

| Junction Temperature                   | TJ               | -40  |      | 125      | °C         |

| Storage Temperature                    | T <sub>STG</sub> | -40  |      | 125      | $^{\circ}$ |

### Recommended Operating Conditions

| PARAMETER                              | Symbol | CONDITION | MIN | TYP | MAX  | UNIT |

|----------------------------------------|--------|-----------|-----|-----|------|------|

| Power supply voltage for AVDD          | AVDD   |           | 3   | 3.3 | 3.6  | V    |

| Power supply voltage for PVDD          | PVDD   |           | 4.5 |     | 6.5  | V    |

| Power supply voltage for DVDD          | DVDD   |           | 3   | 3.3 | 3.6  | V    |

| Ambient Operating Temperature          | Ta     |           | -25 | 25  | 85   | Ç    |

| DVDD Referenced Digital Input Voltages | Vı     |           | 0   |     | DVDD | V    |

| Minimum Speaker Load                   | R∟     | PVDD<5V   | 2   |     |      | Ω    |

| Millimum Speaker Load                  | KL     | PVDD<6.5V | 3.6 |     |      | Ω    |

#### I/O pins

| PARAMETER                                                     | Symbol | CONDITION                                             | MIN | TYP | MAX | UNIT  |

|---------------------------------------------------------------|--------|-------------------------------------------------------|-----|-----|-----|-------|

| Input Logic High threshold for DVDD referenced digital inputs | VIH1   |                                                       | 70  |     |     | %DVDD |

| Input Logic LOW threshold for DVDD Referenced Digital Inputs  | VIL1   | All Digital I/O pins including \FAULT, \SD, SDA, SCL, |     |     | 30  | %DVDD |

| Input Logic HIGH Current Level                                | IIH1   | ADR0, ADR1, MCLK,                                     |     |     | 15  | uA    |

| Input Logic LOW Current Level                                 | IIL1   | SCLK, SDIN, LRCK                                      |     |     | -15 | uA    |

| Output Logic LOW Voltage Level                                | Voн    |                                                       | 90  |     |     | %DVDD |

| Output Logic LOW Voltage Level                                | Vol    |                                                       |     |     | 10  | %DVDD |

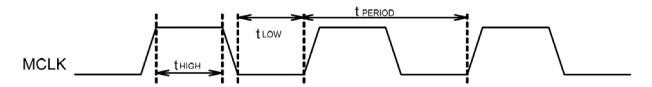

### Master Clock

| PARAMETER                   | Symbol            | CONDITION                                | MIN  | TYP | MAX | UNIT |

|-----------------------------|-------------------|------------------------------------------|------|-----|-----|------|

| Allowable MCLK Duty Cycle   | D <sub>MCLK</sub> |                                          | 45   | 50  | 55  | %    |

| Supported MCLK Frequencies  | f <sub>MCLK</sub> | Values include: 128, 192, 256, 384, 512. | 128  |     | 512 | fs   |

| Pulse duration of MCLK high | t <sub>HIGH</sub> |                                          | 10.1 |     |     | ns   |

| Pulse duration of MCLK low  | t <sub>LOW</sub>  |                                          | 10.1 |     |     | ns   |

| Period of MCLK              | tperiod           |                                          | 20.2 |     |     | ns   |

-5- 6/2021 – V0.1

<sup>&</sup>lt;sup>1</sup> Depending on parts and PCB layout, characteristics may be changed.

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

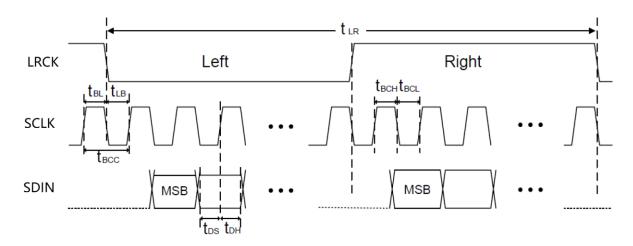

### Serial Audio Port

| PARAMETER                                                | Symbol           | CONDITION                     | MIN | TYP                 | MAX | UNIT |

|----------------------------------------------------------|------------------|-------------------------------|-----|---------------------|-----|------|

| Allowable SCLK Duty Cycle                                | Dsclk            |                               | 45  | 50                  | 55  | %    |

| Supported Input Sample Rates (1/t <sub>LR</sub> )        | fs               |                               | 8   |                     | 192 | kHz  |

| Required LRCK to SCLK Rising Edge                        | t <sub>LB</sub>  |                               | 15  |                     |     | ns   |

| Required SCLK Rising Edge to LRCK edge                   | t <sub>BL</sub>  |                               | 15  |                     |     | ns   |

| Supported SCLK Frequencies (1/t <sub>BCC</sub> ) for I2S | Fsclk            | Values include:<br>32, 48, 64 | 32  |                     | 64  | fs   |

| Supported SCLK Frequencies (1/t <sub>BCC</sub> ) for TDM | Fsclk            | Values include: 128, 256, 512 | 128 |                     | 512 | fs   |

| SCLK Pulse Width High                                    | t <sub>BCL</sub> |                               |     | t <sub>BCC</sub> /2 |     |      |

| SCLK Pulse Width Low                                     | tвсн             |                               |     | t <sub>BCC</sub> /2 |     |      |

| Required SDIN Hold Time after SCLK, Rising Edge          | t <sub>DH</sub>  |                               | 15  |                     |     | ns   |

| Required SDIN Setup Time before SCLK Rising Edge         | t <sub>DS</sub>  |                               | 15  |                     |     | ns   |

### Protection Circuitry

| PARAMETER                                       | Symbol             | CONDITION    | MIN | TYP | MAX | UNIT       |

|-------------------------------------------------|--------------------|--------------|-----|-----|-----|------------|

| PVDD Undervoltage Error Threshold               | UVERTH             | PVDD Falling |     | 2.1 |     | V          |

| PVDD Undervoltage Error Threshold               | UVE <sub>FTH</sub> | PVDD Rising  |     | 1.9 |     | V          |

| Overtemperature Error Threshold                 | ОТЕтн              |              |     | 150 |     | $^{\circ}$ |

| Overtemperature Error Hysteresis                | OTEHYS             |              |     | 15  |     | °C         |

| Overcurrent Error Threshold for each BTL Output | ОСЕтн              |              |     | 3.5 |     | Α          |

### Speaker Amplifier in All Modes

| PARAMETER                             | Symbol                  | CONDITION                 | MIN | TYP | MAX | UNIT |

|---------------------------------------|-------------------------|---------------------------|-----|-----|-----|------|

| Speaker Amplifier Gain                | AV <sub>00</sub>        |                           |     | 26  |     | dBV  |

| Speaker Amplifier DC Offset           | Vos                     | BTL                       |     | 5   |     | mV   |

| Speaker Amplifier Switching Frequency | f <sub>SPK_AMP(1)</sub> |                           |     | 480 |     | kHz  |

|                                       |                         | f <sub>S</sub> = 44.1 kHz |     | 3.7 |     | Hz   |

| –3-dB Corner Frequency of High-Pass   | <b>f</b> _              | f <sub>S</sub> = 48 kHz   |     | 4   |     | Hz   |

| Filter                                | f <sub>C</sub>          | fs = 88.2 kHz             |     | 7.4 |     | Hz   |

|                                       |                         | f <sub>S</sub> = 96 kHz   |     | 8   |     | Hz   |

### • Speaker Amplifier in Stereo Bridge Tied Load (BTL) Mode

TA = 25°, PVDD = 5V, DVDD = AVDD = 3.3V, BTL mode, GAIN = 26dBV, BD mode, fs = 48kHz (unless otherwise noted)

| PARAMETER                                               | Symbol | CONDITION                                                                       | MIN | TYP  | MAX | UNIT |

|---------------------------------------------------------|--------|---------------------------------------------------------------------------------|-----|------|-----|------|

| Idle Channel<br>Noise                                   | VN     | GAIN =16dBV, R <sub>SPK</sub> = 8 $\Omega$ or 4 $\Omega$ , 20-20kHz, A-Weighted |     | 100  |     | μV   |

| Signal to Noise<br>Ratio<br>(Referenced to<br>THD+N=1%) | SNR    | $R_{\text{SPK}}$ = 8 $\Omega$ or $4\Omega,$ Gain = 16dBV, 20-20kHz, A-Weighted  |     | 88   |     | dB   |

| Maximum                                                 |        | PVDD = 5 V, R <sub>SPK</sub> = 4 Ω, THD+N = 1%                                  |     | 1.95 |     | W    |

| Instantaneous                                           | De     | PVDD = 5 V, R <sub>SPK</sub> = 8 Ω, THD+N = 1%                                  |     | 1.2  |     | W    |

| Output Power                                            | Po     | PVDD = 5V, R <sub>SPK</sub> = 4 Ω, THD+N = 1%                                   |     | 2.5  |     | W    |

| Per. Ch.                                                |        | PVDD = 5V, R <sub>SPK</sub> = 8 Ω, THD+N = 1%                                   |     | 1.6  |     | W    |

| Total Harmonic<br>Distortion and<br>Noise               | THD+N  | PVDD = 5 V, R <sub>SPK</sub> = 4 Ω, Po = 1 W                                    |     | 0.08 |     | %    |

### Typical current consumption

TA = 25°, PVDD = 12V, DVDD = AVDD = 3.3V, No Load, BTL mode, GAIN = 20dBV, BD mode, fs = 48kHz, (unless otherwise noted)

| PARAMETER                                | Symbol                 | CONDITION                             | MIN | TYP | MAX | UNIT |

|------------------------------------------|------------------------|---------------------------------------|-----|-----|-----|------|

| I <sub>DVDD+AVDD</sub>                   |                        |                                       |     |     |     |      |

|                                          |                        | fs=48kHz<br>MCLK=128*fs               |     | 4.5 |     | mA   |

|                                          |                        | fs=48kHz<br>MCLK=256*fs               |     | 5.3 |     | mA   |

| Quiescent current in DVDD+AVDD           | lavas visa             | fs=48kHz<br>MCLK=512*fs               |     | 5.5 |     | mA   |

| Quiescent cunent in DVDD+AVDD            | I <sub>DVDD+AVDD</sub> | fs=32kHz<br>MCLK=128*fs               |     | 6.7 |     | mA   |

|                                          |                        | fs=32kHz<br>MCLK=256*fs               |     | 8.3 |     | mA   |

|                                          |                        | fs=32kHz<br>MCLK=512*fs               |     | 8.8 |     | mA   |

| DVDD+AVDD current consumption in sleep   | IDVDD+AVDD_SL          | SLEEP = H,<br>fs=48kHz<br>MCLK=256*fs |     | 3.0 |     | mA   |

| mode                                     | EEP                    | SLEEP = H,<br>fs=32kHz<br>MCLK=256*fs |     | 3.5 |     | mA   |

| DVDD+AVDD current consumption in SD mode | IDVDD+AVDD_SD          | \SD = L,<br>No clock                  |     | 120 |     | uA   |

| IPVDD                                    |                        |                                       |     |     |     |      |

| Quiescent current in PVDD                | IPVDD                  | PVDD=5V                               |     | 3   |     | mA   |

| PVDD current consumption in SD mode      | I <sub>PVDD_SD</sub>   | PVDD=V                                |     | 0.1 |     | uA   |

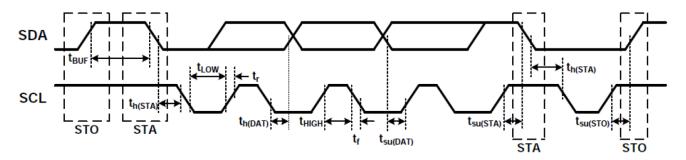

### ● I<sup>2</sup>C Control Port

| DADAMETED                                                                                    | Cumbal               | Sta | Standard-Mode |                                  |     | Fast-Mode |                                  |      |  |

|----------------------------------------------------------------------------------------------|----------------------|-----|---------------|----------------------------------|-----|-----------|----------------------------------|------|--|

| PARAMETER                                                                                    | Symbol               | MIN | TYP           | MAX                              | MIN | TYP       | MAX                              | UNIT |  |

| Allowable Load Capacitance for Each I <sup>2</sup> C Line                                    | Сь                   |     |               | 400                              |     |           | 400                              | pF   |  |

| Support SCL frequency                                                                        | f <sub>SCL</sub>     |     |               | 100                              |     |           | 400                              | kHz  |  |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated. | th(STA)              | 4   |               |                                  | 0.6 |           |                                  | us   |  |

| Required Pulse Duration, SCL HIGH                                                            | t <sub>HIGH</sub>    | 4   |               |                                  | 0.6 |           |                                  | us   |  |

| Required Pulse Duration, SCL LOW                                                             | tLOW                 | 4.7 |               |                                  | 1.3 |           |                                  | us   |  |

| Setup time for a repeated START condition                                                    | t <sub>su(STA)</sub> | 4.7 |               |                                  | 0.6 |           |                                  | us   |  |

| Data hold time                                                                               | t <sub>h(DAT)</sub>  | 0   |               | 3.45                             | 0   |           | 0.9                              | us   |  |

| Setup Time, SDA to SCL                                                                       | t <sub>su(DAT)</sub> | 250 |               |                                  | 100 |           |                                  | ns   |  |

| Rise Time, SCL                                                                               | Tr_SCL               |     |               | 1000                             |     |           | 300                              | ns   |  |

| Rise Time, SDA                                                                               | $T_{r\_SDA}$         |     |               | 1/(4*f <sub>scl</sub> )-<br>0.25 |     |           | 1/(4*f <sub>scl</sub> )<br>-0.25 | us   |  |

| Fall Time, SCL and SDA                                                                       | $T_f$                |     |               | 300                              |     |           | 300                              | ns   |  |

| Setup Time, SCL to STOP condition                                                            | t <sub>su(STO)</sub> | 4   |               |                                  | 0.6 |           |                                  | us   |  |

| Bus Free time between STOP and START conditions                                              | t <sub>BUF</sub>     | 4.7 |               |                                  | 1.3 |           |                                  | us   |  |

### **■ TYPICAL OPERATING CHARACTERISTICS**

To be continued

-9- 6/2021 – V0.1

#### APPLICATION INFORMATION

The HT513 is a flexible and easy-to-use stereo class-D speaker amplifier with an digital input serial audio port. The HT513 supports a variety of audio clock between 8kHz to 192kHz sample rate.

HT513 是一颗简单易用且灵活的数字输入 D类音频功放,其支持8k~192kHz的采样频率。

#### **Power Supplies** 1

Only two power supplies are required for the HT513. They are a 3.3-V power supply, called DVDD and AVDD for the small signal digital and analog and a higher voltage power supply, called PVDD for the output stage of the speaker. To enable use in a variety of applications, PVDD can be operated over a large range of voltages, which is 2.5-6.5V.

HT513 仅需要两种电源供电,即在 DVDD (数字电源)和 AVDD(模拟电源)端加 3.3V, 在 PVDD (功率电源) 端加 2.5-6.5V。。

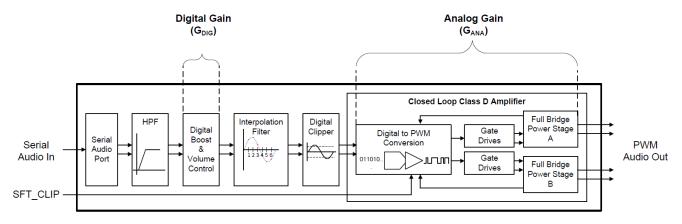

#### 2 Speaker Amplifier Audio Signal Path

Figure 1 Speaker Amplifier Audio Signal Path

#### 2.1 **Serial Audio Port**

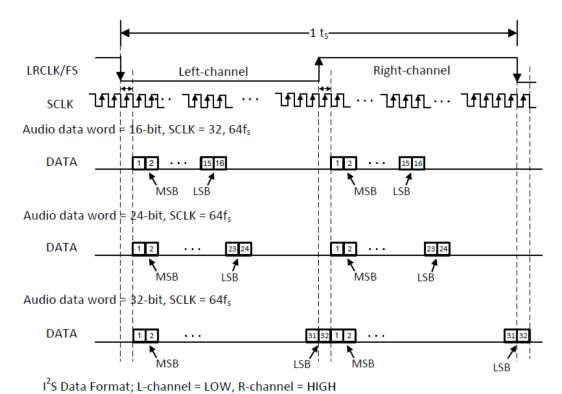

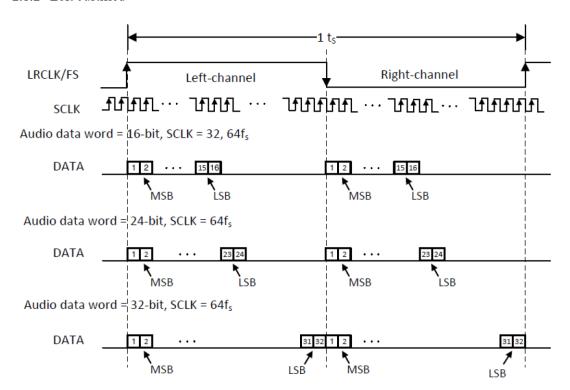

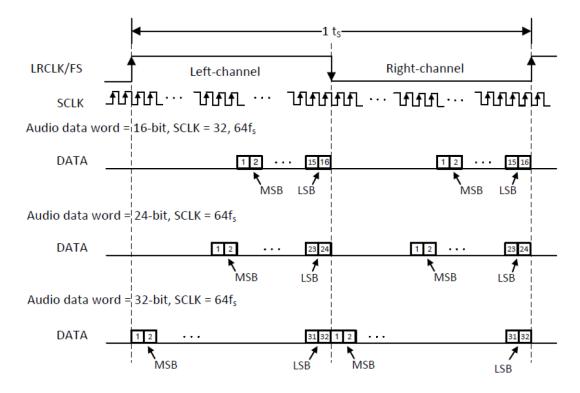

The serial audio port receives audio in either I<sup>2</sup>S, Left Justified, Right Justified or TDM formats, up to 32-bit word length. Default setting is I<sup>2</sup>S and 32-bit word length. The supported clock rates and ratios are detailed below.

HT513 的数字音频串行输入接口支持 I2S、

左对齐、右对齐、TDM 等数据格式,最高支持 32 bit 字长(SCLK = 32×2 fs)。默认设置为 I<sup>2</sup>S、 32 bit 字长。支持的相关时钟速率和比例如下表。

| Maximum Sample Rate fs (kHz) | SCLK Rate (xfs) |

|------------------------------|-----------------|

| 8-48kHz                      | 128, 256, 512   |

| 96kHz                        | 128, 256        |

| 192kHz                       | 128             |

Table1 Supported SCLK rates for TDM

#### Table2 Supported SCLK rates for IIS/LJ/RJ

| Sample  |            | MCLK rate (× fs) |            |            |            |            |            |            |  |  |  |  |

|---------|------------|------------------|------------|------------|------------|------------|------------|------------|--|--|--|--|

| Rate fs | 128        | 192              | 256        | 384        | 512        | 768        | 1024       | 1152       |  |  |  |  |

| (kHz)   |            |                  |            | SCLK r     | ate (× fs) |            |            |            |  |  |  |  |

| 8       | N/S        | N/S              | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | N/S        | N/S        |  |  |  |  |

| 12      | N/S        | N/S              | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | N/S        | N/S        |  |  |  |  |

| 16      | N/S        | N/S              | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | N/S        |  |  |  |  |

| 24      | N/S        | N/S              | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | N/S        |  |  |  |  |

| 32      | 32, 48, 64 | 32, 48, 64       | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 |  |  |  |  |

| 38      | 32, 48, 64 | 32, 48, 64       | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | N/S        |  |  |  |  |

| 44.1    | 32, 48, 64 | 32, 48, 64       | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | N/S        |  |  |  |  |

| 48      | 32, 48, 64 | 32, 48, 64       | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | N/S        |  |  |  |  |

| 64      | 32, 48, 64 | 32, 48, 64       | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | 32, 48, 64 | N/S        | N/S        |  |  |  |  |

| 88.2    | 32, 48, 64 | 32, 48, 64       | 32, 48, 64 | 32, 48, 64 | N/S        | N/S        | N/S        | N/S        |  |  |  |  |

| 96      | 32, 48, 64 | 32, 48, 64       | 32, 48, 64 | 32, 48, 64 | N/S        | N/S        | N/S        | N/S        |  |  |  |  |

| 128     | 32, 48, 64 | 32, 48, 64       | 32, 48, 64 | 32, 48, 64 | N/S        | N/S        | N/S        | N/S        |  |  |  |  |

| 176.4   | 32, 48, 64 | 32, 48, 64       | N/S        | N/S        | N/S        | N/S        | N/S        | N/S        |  |  |  |  |

| 192     | 32, 48, 64 | 32, 48, 64       | N/S        | N/S        | N/S        | N/S        | N/S        | N/S        |  |  |  |  |

### $2.1.1 I^2S$

Figure 2 IIS Audio Data Format Timing

#### 2.1.2 Left-Justified

Figure 3 Left-Justified Audio Data Format Timing

### 2.1.3 Right-Justified

Figure 4 Right-Justified Audio Data Format Timing

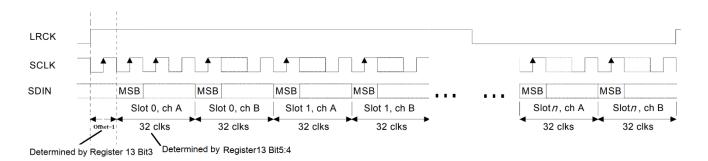

#### 2.1.4 TDM

Figure 5 TDM Audio Data Format Timing

-13-

#### 2.2 DC Blocking Filter

Excessive DC content in the audio signal can damage loudspeakers and even small amounts of DC offset in the signal path cause audible artifacts when muting and unmuting the speaker amplifier. For these reasons, the amplifier employs DC blocking methods for the speaker amplifier which is a high-pass filter provided at the front of the data path to remove any DC from incoming audio data before it is presented to the audio path. The –3 dB corner frequencies for the filter are specified in the speaker amplifier electrical characteristics table. In Hardware Control mode, the DC blocking filter is active and cannot be disabled. In software Control mode, the filter can be bypassed by writing a 0 to bit 7 of register 0x14.

音频信号持续的直流成分,可能损坏喇叭,或者产生输出直流偏置进而在静音/解除静音时产生噪声。因此,HT513 具有隔直流的方式。

在数据通道前端设置高通滤波器,以在数据输入端去除直流成分。该滤波器的截止频率已在上面参数表中列出。在硬件工作模式,该滤波器不能关闭;在软件控制模式,该滤波器可关闭(0x14 寄存器的 bit7)。

#### 2.3 Digital Boost and Volume Control

Following the high-pass filter, a digital boost block is included to provide additional digital gain if required for a given application as well as to set an appropriate clipping point for a given GAIN configuration. The digital boost block defaults to +0dB and is changeable through bit [1:0] of register 14. In most use cases, the digital boost block will remain unchanged, as the volume control offers sufficient digital gain for most applications. The HT513's digital volume control operates from Mute to 24 dB, in steps of 0.5 dB. The equation below illustrates how to set the 8-bit volume control register at address 0x15/0x16:

DVC [Hex Value] =

$$0xCF + (DVC [dB] / 0.5 [dB])$$

Transitions between volume settings will occur at a rate of 0.5 dB every 8 LRCK cycles to ensure no audible artifacts occur during volume changes. This volume fade feature can be disabled via Bit 4 of Register 0x14.

在高通滤波隔直后是数字增加模块,该模块可为数字信号提供一个附加的数字增益,以适应不同的应用。其默认设置是+0dB,可通过0x14 寄存器的 bit[1:0]修改。在大多数情况下,其设置后不用修改。

HT513 的数字音量控制可通过 0x15 和 0x16 寄存器设置 Mute~+24dB (每步 0.5dB)。下面是如何设置该寄存器的公式:

DVC [Hex Value] = 0xCF + (DVC [dB] / 0.5 [dB])

数字音量的变化速率为 0.5dB/8LRCK,以避免音量突变产生噪声。这种音量渐变的功能可通过 0x14 寄存器的 bit4 关闭。

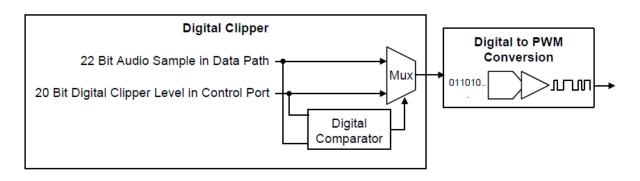

#### 2.4 Digital Clipper

A digital clipper is integrated in the oversampled domain to provide a component-free method to set the clip point of the speaker amplifier. Through the "Digital Clipper Level x" (at register address 0x10, 0x11, 0x12) controls in the I<sup>2</sup>C control port, the point at which the oversampled digital path clips can be set directly, which in turns sets the 10% THD+N operating point of the amplifier. This is useful for applications in which a single system is designed for use in several end applications that have different power rating specifications. Its place in the oversampled domain ensures that the digital clipper is acoustically appealing and reduces or eliminates tones which would otherwise foldback into the audio band during clipping events. Figure 6 shows a block diagram of the digital clipper.

HT513 集成了数字限幅器,无需任何元器件、仅通过寄存器(0x10,0x11,0x12)配置即可设置功放输出的削顶幅度,即功放 10% THD+N工作点。其在一种硬件设计适应多种不同功率等级的应用终端时特别有用。

Figure 6 Digital Clipper Simplified Block Diagram

It is important to note that the actual signal developed across the speaker will be determined not only by the digital clipper, but also the analog gain of the amplifier. Depending on the analog gain settings and the PVDD level applied, clipping could occur as a result of the voltage swing that is determined by the gain being larger than the available PVDD supply rail.

需要了解的是,功放输出的最终幅度不止取决于该限幅器,还取决于当前设置的模拟增益和 PVDD 电压。

#### 2.5 Closed-Loop Class-D Amplifier

Following the digital clipper, the interpolated audio data is next sent to the Closed-Loop Class-D amplifier, whose first stage is Digital to PWM Conversion (DPC) block. In this block, the stereo audio data is translated into two pairs of complimentary pulse width modulated (PWM) signals which are used to drive the outputs of the speaker amplifier. Feedback loops around the DPC ensure constant gain across supply voltages, reduce distortion, and increase immunity to power supply injected noise and distortion. The analog gain is also applied in the Class-D amplifier section of the device.

The switching rate of the amplifier is internally fixed around 480 kHz.

数字信号经过数字限幅器后,进入了闭环 D 类功放。D 类功放的第一级是数字转 PWM 模块 (DPC), PWM 信号则被用来驱动功放输出级。DPC 的反馈环可保证恒定的增益,降低失真,提高对电源噪声的免疫力。该 D 类功放的模拟增益 (GAIN A) 可通过寄存器修改。

D 类功放的开关频率被固定在 480kHz 附近。

#### 3 Speaker Amplifier Protection Suite

The speaker amplifier in the HT513 includes a robust suite of error handling and protection features. It is protected against Over-Current, Under-Voltage, Over-Temperature, and Clock Errors. The status of some errors is reported via the FAULT pin or/and the appropriate error status register in the I<sup>2</sup>C Control Port. Table3 details the types of errors protected by the HT513 Protection Suite and how each are handled.

HT513 具有多种保护功能,包括过流、欠压、过温、时钟错误等保护。某些故障将通过 \FAULT 引脚和/或寄存器错误标志位反应。下表对这些故障和保护进行了详细说明。

Table3 Protection Suite Error Handling Summary

| ERROR                       | CAUSE                                                                                                                                                                               | Reported<br>Method  | The device resumes normal operation                              |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------|--|--|

| Undervoltage Error (UVE)    | PVDD level drops below that specified by UVE <sub>RTH</sub>                                                                                                                         | none                | Immediately resumes after PVDD level returning above $UVE_{RTH}$ |  |  |

| Clock Error (CLKE)          | One or more of the following errors has occurred:  1. Non-supported MCLK to LRCK and/or SCLK to LRCK Ratio;  2. Non-supported MCLK or LRCK rate  3. MCLK, SCLK, or LRCK has stopped | \FAULT and Register | Immediately after Clocks returning to valid state                |  |  |

| Overcurrent Error (OCE)     | Speaker Amplifier output current has increased above the level specified by $OCE_{TH}$                                                                                              | None                | T <sub>fault</sub> after \FAULT pin is pulled low                |  |  |

| Overtemperature Error (OTE) | The temperature of the die has increased above the level specified by the OTE <sub>TH</sub>                                                                                         | none                | T <sub>fault</sub> after \FAULT pin is pulled low                |  |  |

-15-

#### 3.1 \FAULT pin

In both hardware and software Control mode, the \FAULT pin of the HT513 serves as a fault indicator to notify the system that a fault has occurred with the device by being actively pulled LOW. This pin is an open-drain output pin and, unless one is provided internal to the receiver, requires an external pullup to set the net to a known value. The behavior of this pin varies based upon the type of error which has occurred.

在硬件工作模式和软件控制模式,HT513的\FAULT 脚作为故障显示,当芯片发生故障时,该引脚拉低。该引脚是开漏结构的输出脚,需要在外部通过电阻上拉至固定电平,或连接至主控I/O。

#### 3.2 Over-Current Protection

The HT513 features over-current conditions against the output stage short-circuit conditions. The amplifier outputs are switched to a Hi-Z state when the short circuit protection latch is triggered. The device will automatically attempt to resume after Tfault. If the over-current condition is still not cleared, the device will again go into protection.

HT513 输出级短路时,发生了过流,此时芯片进入保护状态,功放输出切换到高阻状态。经过 trault 时间后,芯片将自动尝试恢复,若过流状态已消失,芯片恢复;若过流状态仍在,芯片再次进入保护状态。

#### 3.3 Over-temperature Protection

Over-temperature protection on the HT513 device prevents damage to the device when the internal die temperature exceeds  $150^{\circ}$ C. This triggering point has a  $\pm 15^{\circ}$ C tolerance from device to device. Once the die temperature exceeds the thermal triggering point, the device is switched to the shutdown state and the outputs are disabled. The device will automatically attempt to resume after Tfault. If the over-temperature condition is still not cleared, the device will again go into protection.

过温保护在芯片内部结温达到 150℃时发生,以防止芯片损坏,此时芯片进入关断状态。 经过 tFAULT 时间后,芯片将自动尝试恢复,若过温状态已消失,芯片恢复,若过温状态仍在,芯片再次进入保护状态。

#### 3.4 Under-voltage Protection

When the voltage on PVDD pin falls below the undervoltage threshold, the UVP circuit puts the device into shutdown mode. The device recovers automatically once the under-voltage condition has been removed.

#### 3.5 Clock error detection

When any clock of MCLK, SCLK, LRCK halt or shifted to a non-supported speed, the device reports Clock Error in bit [1:0] of Register 0x17 and \Fault pin. The device recovers automatically once the clock-error condition has been removed.

当 MCLK、SCLK、LRCK 停止或为不支持的速率时,芯片进入保护状态,\FAULT 脚拉低,寄存器 0x17 的 bit[1:0]标志位进行相应显示。当故障撤销时,芯片立即自动恢复,\FAULT 恢复高,寄存器标志位恢复。

当 PVDD 电压低于欠压保护点(UVE<sub>FTH</sub>)

时,芯片进入保护状态,芯片关闭。当 PVDD 高

于欠压保护点(UVERTH)后,芯片立即自动恢

复。

#### 4 Device Functional Modes

#### 4.1 Software Control and Hardware Control

The HT513 device can be configured via an I<sup>2</sup>C communication port which is software control mode. Once all powers (PVDD, AVDD, DVDD) are brought up and stable, the device is ready for software control. Before the device is configured into operation (that is bring \SD pin to high, or write Bit "SD" into 1), configure the device via I<sup>2</sup>C in the manner required by the use case, e.g., bit "Format".

For systems which do not require the added flexibility of the I<sup>2</sup>C control port or do not have an I<sup>2</sup>C host controller, the HT513 can be used directly in Hardware Control Mode with default configurations. The only external I/O that can be controlled in Hardware Control Mode is the \SD pin.

#### 4.2 Speaker Amplifier Shut Down (\SD pin)

The \SD pin is provided to place the speaker amplifier into shutdown. Driving this pin LOW will place the device into shutdown, while pulling it HIGH will bring the device into operation. The shutdown mode is the lowest power consumption mode that the device can be placed in while the power supplies are up.

However, when \SD pin is pulled low, the software control mode is ready, the device is still capable of being configured through I<sup>2</sup>C port. If the \SD pin is pulled low, and bit SD is written into 1, the device is in operation mode. See as the following table.

HT513 可以通过 I<sup>2</sup>C 通讯端口进行配置,即软件控制模式。当 PVDD、AVDD、DVDD 已稳定,芯片的软件控制模式即已准备就绪。在芯片进入工作状态(即将\SD 脚拉高,或将 Bit "SD"写 1)前,需要通过 I<sup>2</sup>C 将芯片配置成需要的状态(如 bit "Format"等)。

对于不需要灵活的配置,或没有 I<sup>2</sup>C 主机的应用,HT513 可工作在硬件模式,此时芯片工作在默认配置,外部唯一可控制的端口即为\SD。

\SD 脚拉低时,芯片进入关断模式;\SD 拉高时,芯片进入工作状态。在关断模式下,芯片进入低功耗状态。

需要注意的是,\SD 拉低时,芯片的软件控制模式仍处于准备就绪状态,芯片仍可通过 I<sup>2</sup>C 控制,此时若将 Bit SD 写 1,芯片仍可进入工作状态。如下表。

#### Table4 \SD pin and Bit SD

| \SD pin | Bit SD | Mode             |

|---------|--------|------------------|

| LOW     | 1      | Normal operation |

| LOW     | 0      | Shutdown mode    |

| High    | 0      | Normal operation |

| High    | 1      | Normal operation |

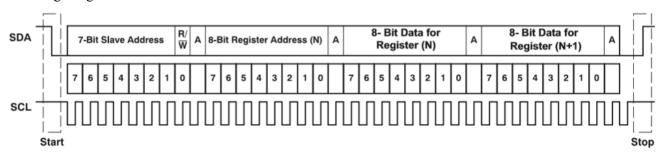

#### 4.3 I<sup>2</sup>C Control Port

#### 4.3.1 I<sup>2</sup>C Device Address

Each device on the I<sup>2</sup>C bus has a unique address that allows it to appropriately transmit and receive data to and from the I<sup>2</sup>C master controller. As part of the I<sup>2</sup>C protocol, the I<sup>2</sup>C master broadcast an 8-bit word on the bus that contains a 7-bit device address in the upper 7 bits and a read or write bit for the LSB. The HT513 has a configurable I<sup>2</sup>C address. The ADR[1:0] can be used to set the device address of the HT513. The I<sup>2</sup>C device address is configured as "110110x [R/W]", where "x" corresponds to the state of the ADR pin at first power up sequence of the device. [R/W] represents 0 when writing, [R/W] represents 1 when reading.

每个器件在 I<sup>2</sup>C 总线上具有一个独一无二的器件地址,以便正确的将数据传输至 I<sup>2</sup>C 主机及从 I<sup>2</sup>C 主机接收数据。作为 I<sup>2</sup>C 协议的一部分,I<sup>2</sup>C 主机在总线上广播一个 8 位字节,该字节包含高 7 位的 7 位设备地址和 LSB 的读或写位。HT513 通过引脚 ADR 可设置 I<sup>2</sup>C 地址。I<sup>2</sup>C 地址即为 110110x [R/W],其中"x"表示上电时引脚 ADR 的状态,当进行读操作时[R/W]代表 1,当进行写操作时[R/W]代表 0。

6/2021 - V0.1

-17-

#### 4.3.2 General Operation of the I<sup>2</sup>C Control Port

The HT513 device has a bidirectional I<sup>2</sup>C interface that is compatible with the Inter IC (I<sup>2</sup>C) bus protocol and supports both 100-kHz and 400-kHz data transfer rates. This is a slave-only device that does not support a multi-master bus environment or wait-state insertion.

The I<sup>2</sup>C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system using serial data transmission. The address and data 8-bit bytes are transferred most-significant bit (MSB) first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data terminal (SDA) while the clock is at logic high to indicate start and stop conditions. A high-to-low transition on SDA indicates a start, and a low-to-high transition indicates a stop. Normal data-bit transitions must occur within the low time of the clock period.

The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then waits for an acknowledge condition. The device holds SDA low during the acknowledge clock period to indicate acknowledgment. When this occurs, the master transmits the next byte of the sequence. Each device is addressed by a unique 7-bit slave address plus R/W bit (1 byte). All compatible devices share the same signals via a bi-directional bus using a wired-AND connection.

Use external pull-up resistors for the SDA and SCL signals to set the logic-high level for the bus.

HT513 I<sup>2</sup>C 接口支持双向传输,该接口与 I<sup>2</sup>C 总线协议兼容,并支持 100 kHz 和 400 kHz 数据传输速率。这是一个从设备,不支持多主机的总线环境,及等待状态下的插入。

I<sup>2</sup>C 总线具有两个信号, SDA(数据)和 SCL (时钟), 在系统中的器件之间使用串行数据传输进行通信。地址和数据的 8 位字节首先传输最高有效位 (MSB)。此外,总线上传输的每个字节由接收设备用确认位 (ACK) 进行确认。每个传输操作从主设备驱动总线上的启动条件开始,并以主设备驱动总线上的停止条件结束。当时钟处于逻辑高电平时,总线使用数据终端 (SDA)上的转换来指示启动和停止条件。SDA 上的高到低转换表示开始,低到高转换表示停止。正常的数据位转换必须在时钟为低时发生。

主机生成7位从机地址和读/写(R/W)位,以打开与另一个设备的通信,然后等待确认条件。在应答时钟周期内,设备保持SDA低,以指示确认。当发生这种情况时,主机发送序列的下一个字节。每个设备有唯一的7位从机地址加上R/W位(1字节)。所有兼容设备通过并联的总线共享信息。

SDA 和 SCL 需通过外部上拉电阻截至逻辑高电平。

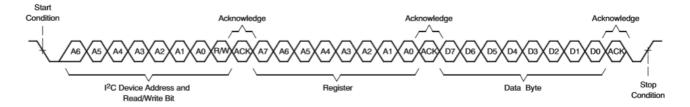

Figure 7 Typical I<sup>2</sup>C Sequence

Figure 8 Single-Byte Write Transfer

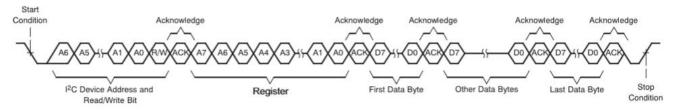

#### Figure 9 Multiple-Byte Write Transfer

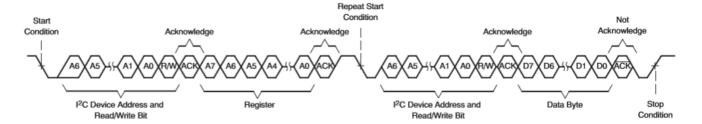

Figure 10 Single-Byte Read Transfer

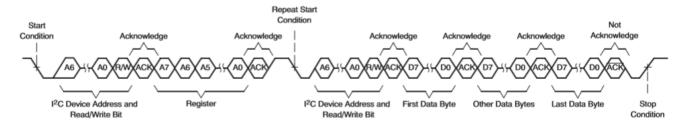

Figure 11 Multiple-Byte Read Transfer

#### 5 Register Map

#### Table5 Register Map

| Register | Bit7                                 | Bit6              | Bit5             | Bit4           | Bit3       | Bit2     | Bit1      | Bit0       | Default<br>Value |

|----------|--------------------------------------|-------------------|------------------|----------------|------------|----------|-----------|------------|------------------|

| 0x10     | Digital Clipper Level DigClip[19:12] |                   |                  |                |            |          |           |            |                  |

| 0x11     | Digital Clipper Level DigClip[11:4]  |                   |                  |                |            |          |           |            |                  |

| 0x12     | ı                                    | Digital Clipper L | evel DigClip[3:0 | ]              | SLEEP      | SD       | MUTE_A    | SPEED      | F0h              |

| 0x13     | Data F                               | ormat             | Word_            | Length         | TDM_Offset | TDM_Slot |           | TDM_Slot   |                  |

| 0x14     | HPF Byps                             | Mix               | Reserved         | Fade           | MUTE       | Reserved | Digital   | Boost      | 90h              |

| 0x15     |                                      |                   |                  | volume         | control    |          |           |            | CFh              |

| 0x16     |                                      |                   |                  | Rese           | erved      |          |           |            | CFh              |

| 0x17     | ch_Shift                             | Fade_Mode         | SCLK_DET<br>_EN  | CLK_DET_<br>EN | Reserved   |          | CLK_Error | SCLK_Error | 33h              |

| 0x18     | Reserved                             |                   | Analog Gain      |                | Reserved   |          |           |            | 02h              |

| 0x19     | Modulation                           |                   | Spread Spectrur  | n              |            | Reserved |           | Gain_Group | 70h              |

The register details are as follows. The blue fonts are the default settings when powering on.

寄存器详细信息如下。蓝色字体为上电时的默认设置状态。

### Register Address: 0x10 (default FFh)

|   | Bit | R/W | Label          | Default | Description                                                                                                                                                 |

|---|-----|-----|----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | 7:0 | R/W | DigClip[19:12] | FFh     | The digital clipper level is decoded from 3 registers: DigClip[19:12], DigClip[11:4] and DigClip[3:0]. The default value is the highest value of the level. |

#### Register Address: 0x11 (default FFh)

| Bit | R/W | Label         | Default | Description                                                                                                                                                 |

|-----|-----|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | R/W | DigClip[11:4] | FFh     | The digital clipper level is decoded from 3 registers: DigClip[19:12], DigClip[11:4] and DigClip[3:0]. The default value is the highest value of the level. |

The digital clipper level determined by DigClip[19:0] is the maximum output threshold level from DAC transferring to the analog Amplifier. The default value of the digital clipper level is the full scale of DAC output, and decreasing the value of DigClip[19:0] will decrease the digital clipper level as well.

### Register Address: 0x12 (default F0h)

| Bit | R/W | Label        | Default | Description                                                                                                                                                 |

|-----|-----|--------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | R/W | DigClip[3:0] | 1111    | The digital clipper level is decoded from 3 registers: DigClip[19:12], DigClip[11:4] and DigClip[3:0]. The default value is the highest value of the level. |

| 3   | R/W | SLEEP        | 0       | 0: the device is not in the SLEEP mode;                                                                                                                     |

|     |     |              |         | 1: the device is in the SLEEP mode.                                                                                                                         |

|     |     |              |         | In sleep mode, the analog Amp is muted, and the digital circuit works with lower current dissipation.                                                       |

| 2   | R/W | SD           | 0       | 0: the device is shut down;                                                                                                                                 |

|     |     |              |         | 1: the device is not shut down;                                                                                                                             |

|     |     |              |         | Notice that if the device is truly shutdown also depends on the \SD pin, see <b>Speaker Amplifier</b>                                                       |

|     |     |              |         | Shut Down (\SD pin).                                                                                                                                        |

| 1   | R/W | MUTE_A       | 0       | 0: The analog Amp output is not muted                                                                                                                       |

|     |     |              |         | 1: The analog Amp output is muted                                                                                                                           |

| 0   | R/W | SPEED        | 0       | 0: Serial Audio Port will accept sample rates between 8k – 96kHz                                                                                            |

|     |     |              |         | 1: Serial Audio Port will accept sample rates between 96kHz-192kHz                                                                                          |

### Register Address: 0x13 (default 00h)

| Bit | R/W | Label       | Default | Description                                                                                                                                                                                                        |

|-----|-----|-------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | R/W | Format      | 00      | Control the Serial Audio Port data format                                                                                                                                                                          |

|     |     |             |         | 00: I <sup>2</sup> S                                                                                                                                                                                               |

|     |     |             |         | 01 : Left justified                                                                                                                                                                                                |

|     |     |             |         | 10: Rright justified                                                                                                                                                                                               |

|     |     |             |         | 11: TDM                                                                                                                                                                                                            |

| 5:4 | R/W | Word_Length | 00      | Control the Serial Audio Port sample word length                                                                                                                                                                   |

|     |     |             |         | 00: 32bits                                                                                                                                                                                                         |

|     |     |             |         | 01: 24 bits                                                                                                                                                                                                        |

|     |     |             |         | 10: 20bits                                                                                                                                                                                                         |

|     |     |             |         | 11: 16bits                                                                                                                                                                                                         |

| 3   | R/W | TDM_Offset  | 0       | Control the offset of TDM data in the audio frame. The offset is defined as the number of SCLK from starting (MSB) of audio frame to the starting of the desired audio sample, see Figure 5 TDM Audio Data Format. |

|     |     |             |         | 0: offset = 0 SCLK                                                                                                                                                                                                 |

|     |     |             |         | 1: offset = 1 SCLK                                                                                                                                                                                                 |

| 2:0 | R/W | TDM_Slot    | 000     | Control the slot number of TDM data in the audio frame. The slot number is defined as Figure 5 TDM Audio Data Format.                                                                                              |

|     |     |             |         | 000: Slot0_A + Slot0_B;                                                                                                                                                                                            |

|     |     |             |         | 001: Slot1_A + Slot1_B;                                                                                                                                                                                            |

|     |     |             |         |                                                                                                                                                                                                                    |

|     |     |             |         | 111: Slot7_A + Slot7_B;                                                                                                                                                                                            |

### Register Address: 0x14 (default 90h)

| Bit | R/W | Label    | Default | Description                                                          |

|-----|-----|----------|---------|----------------------------------------------------------------------|

| 7   | R/W | HPF Byps | 1       | 0: The internal high-pass filter in the digital path is bypassed     |

|     |     |          |         | 1: The internal high-pass filter in the digital path is not bypassed |

| 6   | R/W | Left_Mix | 0       | 0: mixer is disabled                                                 |

|     |     |          |         | 1: mixer is enabled, so that digital output = 1 / 2(left+right)      |

| 5   | R/W | Reserved | 0       | Reserved, make it always 0                                           |

| 4   | R/W | Fade     | 1       | 0: Volume fading is disabled;                                        |

|     |     |          |         | 1: Volume fading is enabled                                          |

| 3   | R/W | MUTE     | 0       | MUTE the digital output:                                             |

|     |     |          |         | 0: not muted                                                         |

|     |     |          |         | 1: muted                                                             |

| 2   | R/W | Reserved | 0       | Reserved, make it always 0                                           |

| 1:0 | R/W | Dig Bst  | 00      | Digital Boost setting                                                |

|     |     |          |         | 00: +0dB is added to the signal in the digital path                  |

|     |     |          |         | 01: +6dB is added to the signal in the digital path                  |

|     |     |          |         | 10: +12dB is added to the signal in the digital path                 |

|     |     |          |         | 11: +18dB is added to the signal in the digital path                 |

-21-

### Register Address: 0x15 (Default CFh)

| Bit | R/W | Label | Default | Description                                                |

|-----|-----|-------|---------|------------------------------------------------------------|

| 7:0 | R/W | Vol_L | CFh     | Left channel Volume control                                |

|     |     |       |         | 1111,1111: +24dB;                                          |

|     |     |       |         | 1111,1110: 23.5dB                                          |

|     |     |       |         | Gain decreased by 0.5dB every step                         |

|     |     |       |         | 1100,1111: 0dB                                             |

|     |     |       |         | Gain decreased by 0.5dB every step                         |

|     |     |       |         | 0000,0111: -100dB                                          |

|     |     |       |         | Any setting less than 0000,0111 places the channel in MUTE |

### Register Address: 0x16 (Default CFh)

| Bit | R/W | Label    | Default | Description                |

|-----|-----|----------|---------|----------------------------|

| 7:0 | R/W | Reserved | CFh     | Make it the same with 0x15 |

### Register Address: 0x17 (default 33h)

|     | Dit DAM Labat |             |         |                                                                                                                                                                                                            |  |  |

|-----|---------------|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | R/W           | Label       | Default | Description                                                                                                                                                                                                |  |  |

| 7   | R/W           | ch_Shift    | 0       | 0: The left and right channels are not shifted                                                                                                                                                             |  |  |

|     |               |             |         | 1: The left and right channels are shifted                                                                                                                                                                 |  |  |

| 6   | R/W           | Fade_Mode   | 0       | 0: The volume is fading by 0.5dB/8T <sub>LRCK</sub>                                                                                                                                                        |  |  |

|     |               |             |         | 1: The volume is fading by 0.5dB/T <sub>LRCK</sub>                                                                                                                                                         |  |  |

| 5   | R/W           | SCLK_DET_EN | 1       | SCLK error detection, such as SCLK missing detection, SCLK range detection, SCLK/LRCK detection. If error detection is enabled, once any such error is detected, the relevant error flag will change to 1. |  |  |

|     |               |             |         | 0: SCLK error detection is disabled;                                                                                                                                                                       |  |  |

|     |               |             |         | 1: SCLK error detection is enabled.                                                                                                                                                                        |  |  |

| 4   | R/W           | CLK_DET_EN  | 1       | Audio serial port clock error detection, including SCLK, MCLK, LRCK. Once any error such as missing or wrong range of these clocks is detected, the relevant error flag will change to 1.                  |  |  |

|     |               |             |         | 0: CLOCK error detection is disabled;                                                                                                                                                                      |  |  |

|     |               |             |         | 1: CLOCK error detection is enabled.                                                                                                                                                                       |  |  |

| 3:2 | R             | Reserved    | 00      | Unused, make it always 00                                                                                                                                                                                  |  |  |

| 1   | R             | CLK_Error   | 1       | Changes to 0 when Clock Error is detected;                                                                                                                                                                 |  |  |

|     |               |             |         | back to 1 when Clock Error evacuated;                                                                                                                                                                      |  |  |

| 0   | R             | SCLK_Error  | 1       | Changes to 0 when SCLK Error is detected;                                                                                                                                                                  |  |  |

|     |               |             |         | back to 1 when SCLK Error evacuated;                                                                                                                                                                       |  |  |

### Register Address: 0x18 (Default 02h)

| Bit | R/W | Label    | Default | Description                          |                                    |  |  |

|-----|-----|----------|---------|--------------------------------------|------------------------------------|--|--|

| 7   | R   | Reserved | 0       | Unused, make it always 0             | Unused, make it always 0           |  |  |

| 6:4 | R/W | A_GAIN   | 000     | Set analog gain: (Not available yet) |                                    |  |  |

|     |     |          |         | 000: Gain0 = 26dB; Gain1 = 29.3dB    |                                    |  |  |

|     |     |          |         | 010: Gain0 = 20.4dB; Gan1 = 24.1dB   |                                    |  |  |

|     |     |          |         | 100: Gain0 = 17.1dB; Gan1 = 20.9dB   | 101: Gain0 = 15.8dB; Gan1 = 19.6dB |  |  |

|     |     |          |         | 110: Gain0 = 14.7dB; Gan1 = 18.5dB   | 111: Gain0 = 13.7dB; Gan1 = 17.6dB |  |  |

| 3   | R/W | Reserved | 0       | Reserved, make it 0                  |                                    |  |  |

| 2:0 | R   | Reserved | 010     | Unused, make it always 010           |                                    |  |  |

### Register Address: 0x19 (default 70h)

| Bit                             | R/W | Label        | Default | Description                |  |

|---------------------------------|-----|--------------|---------|----------------------------|--|

| 7                               | R/W | Reserved     | 0       | Reserved, make it always 0 |  |

| 6:4 R/W Spread 111 111: Class D |     | 111: Class D |         |                            |  |

|                                 |     |              |         | 010: Class AB              |  |

# HT513

## I<sup>2</sup>S input Class D Amplifier

| 3:1 | R   | Reserved   | 000 | Unused, make it always 000                                                                                             |

|-----|-----|------------|-----|------------------------------------------------------------------------------------------------------------------------|

| 0   | R/W | GAIN_Group | 0   | Select gain group for A_GAIN (Not available yet) (register 0x18, bit [6:4]. 0: Gain0; 1: Gain1                         |

|     |     |            |     | The gain group is only changed when the device is brought from shutdown back into operation after this bit is changed. |

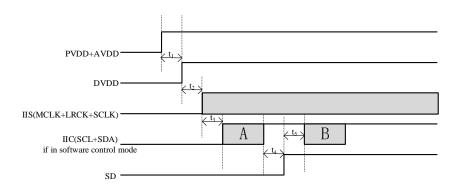

#### **6** Typical Applications

#### **6.1** Startup Procedures

- 1. Configure I/O pins (ADR);

- 2.  $\backslash$ SD pin = Low;

- 3. Bring up power supplies (it does not matter if PVDD, AVDD or DVDD comes up first, provided the device is held in shutdown);

- 4. Once power supplies are stable, start MCLK, SCLK, LRCK;

- 5. Configure the device via the control port in the manner required by the use case; especially bit "Format" (as "A" shown in the following figure).

- 6. Once power supplies and clocks are stable and the control port has been programmed, bring \SD pin High, or write bit "SD" (Bit 2 of Register 0x12) as 1;

- 7. The device is now in normal operation. Fade in SDIN if needed. The device is still configurable through IIC port. (as "B" shown in the following figure)

The sequence diagram is shown in Figure 12 and Table 6.

- 1. 通过引脚ADR设置器件地址;

- 2. \SD脚拉低;

- 3. 接入电源(器件关断状态下, PVDD、AVDD、 DVDD上电先后顺序无严格要求);

- 4. 当电源稳定后,开启MCLK,SCLK,LRCK;

- 5. 通过IIC进行正确的配置,如 "Format"等 (下图中的"A");

- 6. \SD脚拉高,或写bit "SD" 为1 (寄存器 0x12 的Bit 2);

- 7. 器件进入正常工作模式。若需要可将SDIN通 过渐变引入。此后仍可通过IIC进行部分配置。 (下图中的"B")

具体时序如下图 Figure 12和下表Table 6.

Figure 12 Power-on Sequence

Table 6 Recommendations for Power-on Timing

| Symbol | CONDITION | MIN | TYP | MAX | UNIT |

|--------|-----------|-----|-----|-----|------|

| t1     |           | 0   |     |     | ms   |

| t2     |           | 0   |     |     | ms   |

| t3     |           | 1   |     |     | ms   |

| t4     |           | 1   |     |     | ms   |

| t5     |           | 200 |     |     | ms   |

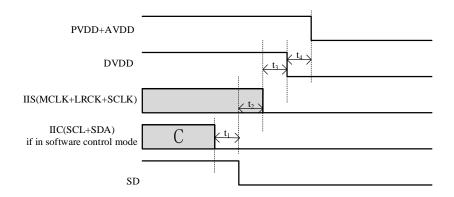

#### 6.2 Power down Procedures

- 1. The device is in normal operation;

- 2. Fade out SDIN if needed; The device is configurable through IIC port before power off;

- 3. Pull \SD pin Low, or write bit "SD" (Bit 2 of Register 0x12) as 0;

Figure 13 and Table7.

- 4. The clocks can be stopped, and power supplies brought down;

- The device is now fully shutdown and powered off.

The sequence diagram is shown in

### 芯片处于工作状态;

- 1. 若需要可将SDIN淡出;器件仍可在关闭之前通过 IIC配置;

- 2. 将\SD脚拉低,或写bit "SD" 为0(寄存器 0x12的 Bit 2);

- 3. MCLK, SCLK, LRCK关闭, 然后电源关闭;

- 4. 芯片已关闭.

具体时序如下图

Figure 13和Table7.

Figure 13 Power-off Sequence

Table 7 Recommendations for Power-off Timing

| Symbol         | CONDITION         | MIN | TYP | MAX | UNIT |

|----------------|-------------------|-----|-----|-----|------|

| t <sub>1</sub> |                   | 1   |     |     | ms   |

| 4.             | Fade-out disabled | 1   |     |     | ms   |

| t <sub>2</sub> | Fade-out enable   | 45  |     |     | ms   |

| t <sub>3</sub> |                   | 1   |     |     | ms   |

| t <sub>4</sub> |                   | 0   |     |     | ms   |

-25- 6/2021 – V0.1

## 7 Typical Circuit Diagram

### ■ PACKAGE OUTLINE

Side View

| Symbol | Dimensions in Millimeters |           |       |  |  |  |  |

|--------|---------------------------|-----------|-------|--|--|--|--|

| Symbol | Min.                      | NOM       | Max.  |  |  |  |  |

| A      | 0.700                     | 0.750     | 0.800 |  |  |  |  |

| A1     | 0.000                     |           | 0.050 |  |  |  |  |

| A2     | 0.195                     | 0.203     | 0.211 |  |  |  |  |

| D      | 3.900                     | 4.000     | 4.100 |  |  |  |  |

| Е      | 3.900                     | 4.000     | 4.100 |  |  |  |  |

| D1     | 2.625                     | 2.650     | 2.675 |  |  |  |  |

| E1     | 2.625                     | 2.650     | 2.675 |  |  |  |  |

| k      |                           | 0.200MIN. | ,     |  |  |  |  |

| b      | 0.200                     | 0.250     | 0.300 |  |  |  |  |

| e      |                           | 0.500TYP. |       |  |  |  |  |

| L      | 0.300                     | 0.400     | 0.500 |  |  |  |  |